IMDEA Networks

Exploiting Multi-Core Parallelism in Blockchain Validation and Construction

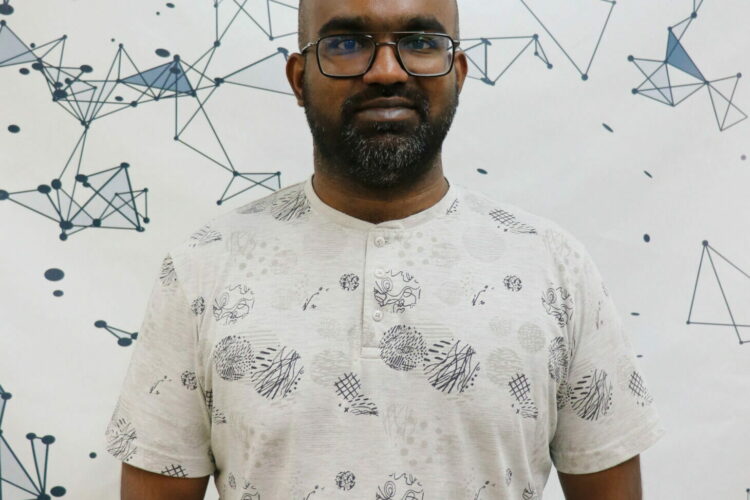

Arivarasan Karmegam, PhD Student at IMDEA Networks Institute, Madrid, Spain

In-house Presentation

Modern blockchains execute each block’s transactions strictly in sequence, leaving substantial multi-core hardware potential unused. Yet, safely parallelizing execution is challenging due to read/write conflicts and validator gas limits. This paper systematically studies how validators can exploit multi-core parallelism during both block execution and block construction without violating blockchain semantics. We formalize two validator-side optimization problems: (i) executing an already ordered block on p cores to minimize makespan, and (ii) selecting and scheduling a subset of mempool transactions under a runtime limit B to maximize validator reward. For both, we develop exact Mixed-Integer Linear Programming (MILP) formulations that capture conflict, order, and capacity constraints, and propose fast deterministic heuristics that scale to realistic workloads. Using Ethereum mainnet traces, we empirically quantify the trade-offs between optimality and runtime. MILPs quickly become intractable as heterogeneity or core count increases, whereas our heuristics execute in milliseconds while achieving near-optimal quality. The heuristics also yield practical throughput and reward gains. The results demonstrate that lightweight, conflict-aware scheduling and selection can unlock substantial parallelism in blockchain validation, bridging the gap between sequential execution and the true potential of multi-core hardware.

About Arivarasan Karmegam

Arivarasan is a PhD student at IMDEA Networks Institute, working with Professor Antonio Fernández Anta. His research focuses on the scalability of distributed ledger technologies. He holds a Bachelor’s degree in Computer Science and Engineering from Anna University and a Master’s degree in Computer Science and Engineering from the Indian Institute of Technology Dhanbad, India.

This event will be conducted in English